先進封裝行業(yè)概覽與先進封裝技術(shù)代表介紹

一、先進封裝行業(yè)概覽

半導(dǎo)體制造產(chǎn)業(yè)主要分為設(shè)計,制造和封測三大環(huán)節(jié)。

上游支撐產(chǎn)業(yè)為EDA、半導(dǎo)體材料和半導(dǎo)體設(shè)備,下游應(yīng)用產(chǎn)業(yè)為消費電子、通訊產(chǎn)業(yè)等。

其中封測行業(yè)屬于半導(dǎo)體晶圓前道制造之后的工序,主要分為封裝和測試兩大細分環(huán)節(jié)。

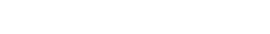

封裝是指將生產(chǎn)加工后的晶圓進行切割、焊線塑封,使電路與外部器件實現(xiàn)連接,并為半導(dǎo)體產(chǎn)品提供機械保護,使其免受物理、化學(xué)等環(huán)境因素損失的工藝。

半導(dǎo)體封裝技術(shù)發(fā)展大致分為四個階段,全球封裝技術(shù)的主流處于第三代的成熟期,主要是CSP、BGA封裝技術(shù),目前封測行業(yè)正在從傳統(tǒng)封裝向先進封裝轉(zhuǎn)型。

隨著半導(dǎo)體先進制程不斷往7nm/5nm,甚至以下邁進,晶片設(shè)計與制造工藝微縮的難度、成本與開發(fā)時間均呈現(xiàn)跳躍式的增長。

面對此難題,晶片業(yè)者試圖透過先進封裝來達到晶片間的高密度互聯(lián),以實現(xiàn)以更低成本提供同等級效能表現(xiàn)。

先進封裝采用了先進的設(shè)計思路和先進的集成工藝,對芯片進行封裝級重構(gòu),并且能有效提升系統(tǒng)高功能密度的封裝技術(shù)。

先進封裝工藝包括倒裝焊(FlipChip)、晶圓級封裝(WLP)、2.5D封裝(Interposer) 、3D封裝 (TSV)、Chiplet等。

芯片整合已演進至2.5D/3D及Chiplet封裝:

二、Chiplet:先進封裝代表

Chiplet又稱芯粒或小芯片,是先進封裝技術(shù)的代表,將復(fù)雜芯片拆解成一組具有單獨功能的小芯片單元 die(裸片),通過 die-to-die 將模塊芯片和底層基礎(chǔ)芯片封裝組合在一起。

Chiplet 實現(xiàn)原理與搭積木相仿,從設(shè)計時就按照不同的計算單元或功能單元對其進行分解,然后每個單元選擇最適合的工藝制程進行制造,再將這些模塊化的裸片互聯(lián)起來,通過先進封裝技術(shù),將不同功能、不同工藝制造的Chiplet封裝成一個系統(tǒng)芯片,以實現(xiàn)一種新形式的 IP 復(fù)用。

Chiplet 的概念源于 Marvell 創(chuàng)始人周秀文博士在 ISSCC 2015 上提出的 Mochi(Modular Chip,模塊化芯片)架構(gòu),伴隨著 AMD 第一個將小芯片架構(gòu)引入其最初的 Epyc 處理器 Naples,Chiplet 技術(shù)快速發(fā)展。

通過Chiplet技術(shù),使用10nm工藝制造出來的芯片,完全也可以達到7nm芯片的集成度,但是研發(fā)投入和一次性生產(chǎn)投入則比7nm芯片的投入要少的多,新的連接形式在其生產(chǎn)過程中帶動設(shè)備需求。

三、晶圓級扇出封裝(FOWLP)

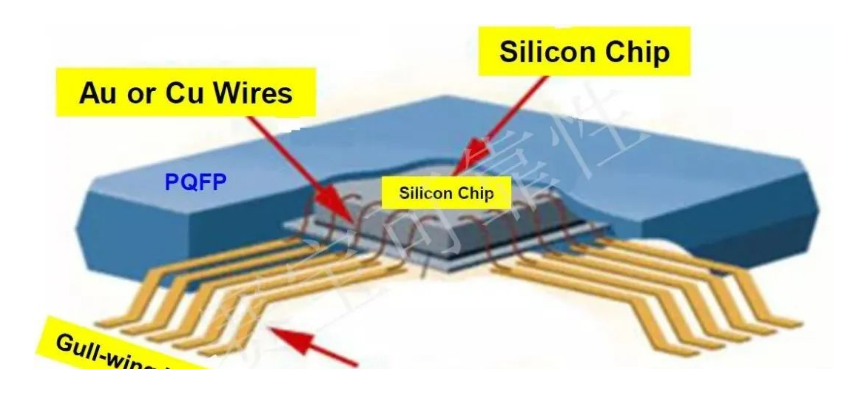

晶圓級扇出封裝在封裝工藝上需要先將晶圓進行切割,挑出KGD(Known Good Die)排列放置于圓型銅質(zhì)載板上,再繼續(xù)后面的封裝步驟。由于有事先切割、挑出KGD及重新配置的步驟,因此晶圓級扇出封裝具有異構(gòu)集成特性,即不同功能的芯片可以組裝在一個封裝中。晶圓級扇入封裝(WLCSP)由于直接在晶圓上完成封裝和測試,然后才切割成單獨的集成電路,因而不具備異構(gòu)集成特性。多個芯片異構(gòu)集成與具有高集成度的單個芯片相比,具有成本低、良率好、產(chǎn)量高等優(yōu)點;與分立的多個單一芯片封裝相比,異構(gòu)集成各芯片之間的互連比PCB布線短、RC延遲低、性能好。異構(gòu)集成不局限于硅片,還可以是MEMS,濾波器和無源器件,從而更好地發(fā)揮扇出的電氣連接優(yōu)勢。

圖2 傳統(tǒng)含有引線框架的封裝

(a) 晶圓級扇出封裝橫截面示意圖

UBM: Under Bump Metalization

RDL: Re-distribution Layer

KGD: Known good die

EMC: Epoxy molding compound

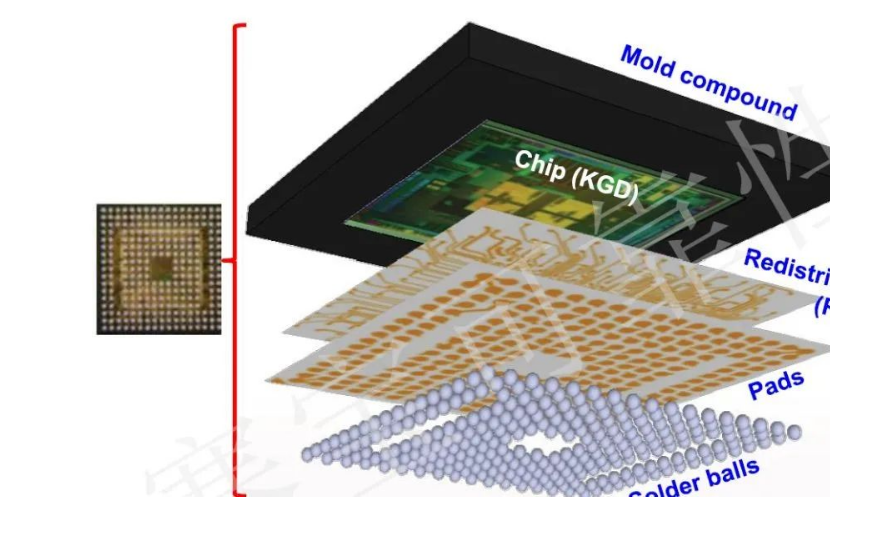

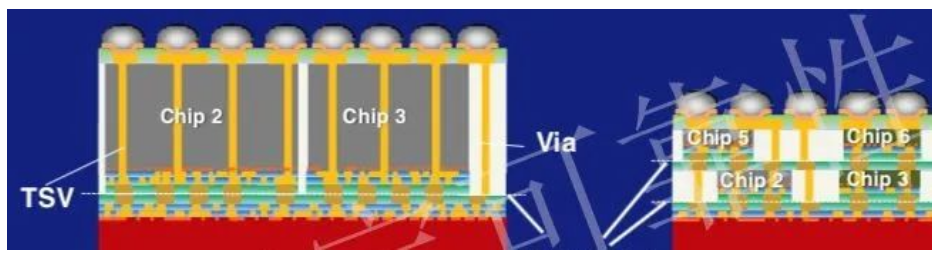

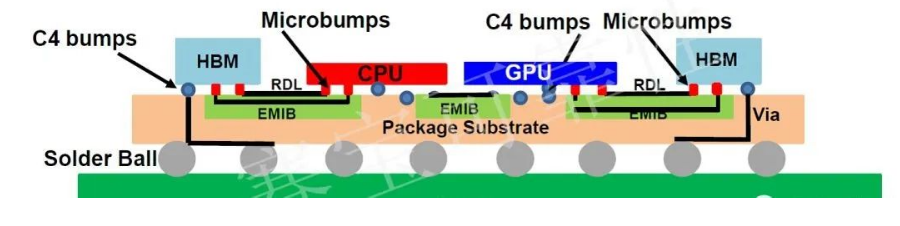

四、2.5D / 3D 封裝

3D與2.5D的區(qū)別在于芯片之間的相對位置是并排還是堆疊,互連方式是水平還是垂直,這個關(guān)鍵區(qū)別決定了3D與2.5D集成密度的不同。早期的3D封裝也是通過引線鍵合形成互連并且連接到引線框架,例如常見的疊層Flash/DDR芯片。為了減少信號損失,提高集成密度,更好地發(fā)揮3D技術(shù)優(yōu)勢,新型3D封裝搭配TSV技術(shù),堆疊的多層芯片通過TSV連接起來。

圖4 典型2.5D封裝

圖5 典型的3D封裝

圖6 含EMIB的3D封裝

五、先進封裝產(chǎn)品清洗劑:

先進封裝產(chǎn)品芯片焊后封裝前,基板載板焊盤上的污染物有多種,可歸納為離子型和非離子型兩大類。離子型污染物接觸到環(huán)境中的濕氣,通電后發(fā)生電化學(xué)遷移,形成樹枝狀結(jié)構(gòu)體,造成低電阻通路,破壞了電路板功能。非離子型污染物可穿透PC B 的絕緣層,在PCB板表層下生長枝晶。除了離子型和非離子型污染物,還有粒狀污染物,例如焊料球、焊料槽內(nèi)的浮點、灰塵、塵埃等,這些污染物會導(dǎo)致焊點質(zhì)量降低、焊接時焊點拉尖、產(chǎn)生氣孔、短路等等多種不良現(xiàn)象。

這么多污染物,到底哪些才是最備受關(guān)注的呢?助焊劑或錫膏普遍應(yīng)用于回流焊和波峰焊工藝中,它們主要由溶劑、潤濕劑、樹脂、緩蝕劑和活化劑等多種成分,焊后必然存在熱改性生成物,這些物質(zhì)在所有污染物中的占據(jù)主導(dǎo),從產(chǎn)品失效情況來而言,焊后殘余物是影響產(chǎn)品質(zhì)量最主要的影響因素,離子型殘留物易引起電遷移使絕緣電阻下降,松香樹脂殘留物易吸附灰塵或雜質(zhì)引發(fā)接觸電阻增大,嚴重者導(dǎo)致開路失效,因此焊后必須進行嚴格的清洗,才能保障電路板的質(zhì)量。

針對先進封裝產(chǎn)品芯片焊后封裝前,基板載板焊盤、電子制程精密焊后清洗的不同要求,合明科技在水基清洗方面有比較豐富的經(jīng)驗,對于有著低表面張力、低離子殘留、配合不同清洗工藝使用的情況,自主開發(fā)了較為完整的水基系列產(chǎn)品,精細化對應(yīng)涵蓋從半導(dǎo)體封裝到PCBA組件終端,包括有水基清洗劑和半水基清洗劑,堿性水基清洗劑和中性水基清洗劑等。具體表現(xiàn)在,在同等的清洗力的情況下,合明科技的兼容性較佳,兼容的材料更為廣泛;在同等的兼容性下,合明科技的清洗劑清洗的錫膏種類更多(測試過的錫膏品種有ALPHA、SMIC、INDIUM、SUPER-FLEX、URA、TONGFANG、JISSYU、HANDA、OFT、WTO等品牌;測試過的焊料合金包括SAC305、SAC307、6337、925等不同成分),清洗速度更快,離子殘留低、干凈度更好。

上一篇:印制電路板清洗質(zhì)量要求

下一篇:先進封裝行業(yè)概覽與先進封裝技術(shù)代表介紹

【閱讀提示】

以上為本公司一些經(jīng)驗的累積,因工藝問題內(nèi)容廣泛,沒有面面俱到,只對常見問題作分析,隨著電子產(chǎn)業(yè)的不斷更新?lián)Q代,新的工藝問題也不斷出現(xiàn),本公司自成立以來不斷的追求產(chǎn)品的創(chuàng)新,做到與時俱進,熟悉各種生產(chǎn)復(fù)雜工藝,能為各種客戶提供全方位的工藝、設(shè)備、材料的清洗解決方案支持。

【免責(zé)聲明】

1. 以上文章內(nèi)容僅供讀者參閱,具體操作應(yīng)咨詢技術(shù)工程師等;

2. 內(nèi)容為作者個人觀點, 并不代表本網(wǎng)站贊同其觀點和對其真實性負責(zé),本網(wǎng)站只提供參考并不構(gòu)成投資及應(yīng)用建議。本網(wǎng)站上部分文章為轉(zhuǎn)載,并不用于商業(yè)目的,如有涉及侵權(quán)等,請及時告知我們,我們會盡快處理;

3. 除了“轉(zhuǎn)載”之文章,本網(wǎng)站所刊原創(chuàng)內(nèi)容之著作權(quán)屬于合明科技網(wǎng)站所有,未經(jīng)本站之同意或授權(quán),任何人不得以任何形式重制、轉(zhuǎn)載、散布、引用、變更、播送或出版該內(nèi)容之全部或局部,亦不得有其他任何違反本站著作權(quán)之行為。“轉(zhuǎn)載”的文章若要轉(zhuǎn)載,請先取得原文出處和作者的同意授權(quán);

4. 本網(wǎng)站擁有對此聲明的最終解釋權(quán)。