因為專業

所以領先

POP封裝在未來的發展趨勢與PoP堆疊芯片清洗介紹

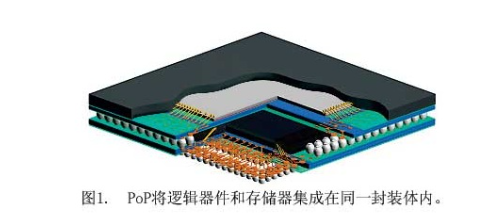

POP(Package on Package)堆疊封裝是一種將多個集成電路(IC)封裝在一起的技術,以實現更小、更輕、更薄的電子設備。在POP封裝中,一個封裝(通常是一個存儲器芯片)被堆疊在另一個封裝(通常是應用處理器)之上,通過焊球連接。這種技術可以提高電路板空間利用率,降低設備的整體尺寸和重量,并提高性能。

一、POP封裝的優點包括:

1. 小型化:通過堆疊多個封裝,可以在有限的空間內實現更多的功能。

2. 高度集成:可以將多種功能的芯片集成在一個封裝內,簡化電路設計。

3. 提高性能:堆疊封裝可以縮短信號傳輸距離,從而提高數據傳輸速度和系統性能。

4. 節省成本:通過減少電路板空間需求,可以降低材料成本和生產成本。

然而,POP封裝也存在一些挑戰,如散熱問題、可靠性問題和制造難度等。因此,在選擇使用POP封裝時,需要綜合考慮這些因素。

二、以下是一些采用了POP封裝技術的電子產品:

1. 智能手機:PoP封裝技術在智能手機領域得到了廣泛的應用。例如,魅族手機16S就采用了PoP封裝技術來集成應用處理器與存儲器。此外,隨著新興應用對集成度、電性能以及超薄化等要求的進一步提高,各家廠商的PoP封裝技術也在不斷創新發展。

2. 新一代可穿戴設備:PoP封裝技術也被廣泛應用于新一代可穿戴設備等領域。

3. 電子手表:隨著電子產品的不斷發展,電子手表也越來越追求體積小便攜,電性能優秀,價格低。封裝技術的發展是電子產品性能提升和價格下降的關鍵因素之一。層疊封裝pop就是一種解決移動設備芯片封裝難題的有效方案。

4. 耳機:例如,魅族POPPro主動降噪耳機就是采用了PoP封裝技術的產品。

5. 健康手表:華米科技發布的全新健康手表”AmazfitPop,售價僅349元,成為市面上最便宜的血氧檢測手表之一。

以上產品都是采用了PoP封裝技術的電子產品。

三、保證PoP封裝的可靠性主要包括以下幾個方面:

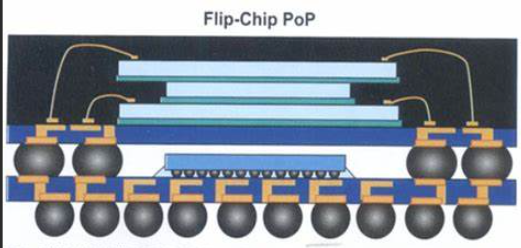

1. SMT工藝的可靠性:PoP的SMT工藝的可靠性是一個重要的關注點。由于錫膏印刷已經不可能在底部元件上完成,頂層CSP元器件這時需要特殊工藝來裝配了,需要將頂層元件浸蘸助焊劑或錫膏后以低壓力放置在底部CSP上。此外,元器件翹曲變形對裝配良率的影響也非常關鍵,翹曲變形可能導致焊點開路。翹曲變形既有來自元件在封裝過程中的變形,也有因為回流焊接過程中的高溫引起的熱變形。

2. 封裝結構的可靠性:PoP封裝的結構相對比較復雜,其散熱問題、封裝材料間熱膨脹系數不匹配造成的熱失配問題及在跌落沖擊載荷下的可靠性問題制約著PoP封裝的進一步發展。在熱循環和濕熱環境下的可靠性研究比較少。在熱循環載荷下,頂部和底部模塊對稱中心最遠端焊點的應力最大,單個焊點呈兩端大中間小的分布趨勢。最大累積等效蠕變應變位于內層焊點,且在芯片邊緣。

3. 封裝材料的可靠性:封裝材料的選擇也會影響PoP封裝的可靠性。例如,AlN、SiC、BeO、Al2O3四種基板材料中,熱膨脹系數最大的BeO基板具有最大的熱疲勞壽命。

4. 封裝測試的可靠性:封裝堆疊PoP作為一種新型的封裝形式,其具有很強的靈活性和擴展性,縮短了產品的上市時間,允許裝配前各模塊單獨測試,保證了更高的良品率。在回流焊載荷下,頂部和底部模塊的最大應力出現在底層芯片的四個邊角,其大小值分別為59.35Mpa和15.6Mpa。在峰值溫度時,頂部和底部模塊的形變分別為10μm和-58μm,兩者的翹曲模式不同,翹曲差值為68μm。

5. 封裝維修的可靠性:PoP封裝的主要作用是在底層封裝中集成高密度的數字或者混合信號邏輯器件,在頂層封裝中集成高密度或者組合存儲器件。但是,維修也比較困難,大多數情況下拆卸下來的芯片基本不能再次利用。

總的來說,保證PoP封裝的可靠性需要從多個方面進行綜合考慮和控制。

四、POP封裝在未來的發展趨勢

1. 超薄化趨勢下的封裝翹曲問題

隨著封裝技術的進一步超薄化,封裝翹曲成為一大問題。封裝中使用了各種不同的材料,如芯片、基板、塑封等,這些材料具有不同的熱膨脹系數(CTE)。當封裝變薄后,鋼性顯著降低,更容易變形,使得翹曲顯著加大。過大的翹曲會使得PoP封裝在表面焊接(SMT)組裝過程中,底層封裝與母板之間,或者底層和上層封裝之間的焊錫球無法連接,出現開路。超薄化的趨勢使得翹曲問題更加突出,成為一個阻礙未來PoP薄化發展的瓶頸。

2. 發展趨勢

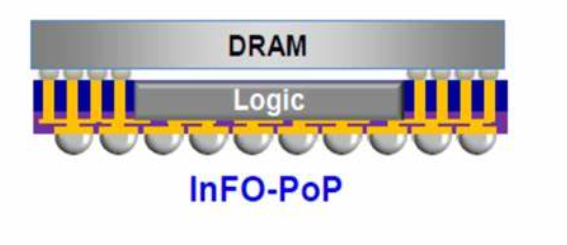

新一代層疊封裝(PoP)的發展趨勢可以概括為:IC集成度進一步提高,芯片尺寸不斷加大,芯片尺寸與封裝尺寸比例不斷提高,使得封裝翹曲也隨之增加。對封裝的電性能要求進一步提高,倒裝芯片技術(flipchip)應用普及,已代替了傳統的焊線(wirebond)技術。同一芯片針對不同應用及客戶要求采用不同封裝尺寸。這些都使得封裝難以采用傳統的統一的材料系統,而必須定制優化。此外,PoP底層和上層之間互連的間距(pitch)縮小,傳統PoP采用0.5mm或以上間距,現在多采用0.4mm間距。不遠的將來,0.3mm間距將出現。間距的縮小使得上下層互連的焊錫高度產生問題。在超薄化趨勢下,PoP封裝的各層材料厚度要求越來越薄。

3. 技術創新與材料優化

為了進一步利用PoP技術的優勢,系統公司可以同芯片供應商與封裝公司合作,對PoP底層或上層元件進一步集成,以滿足其產品需要。例如,基帶芯片和應用處理器芯片可以集成在PoP的底層封裝里。隨著集成度及電性能要求的進一步提高,以及超薄化的需求,PoP封裝技術也不斷發展創新,開始進入新的一代。許多新的PoP技術的開發及新材料的應用也是針對降低封裝翹曲。

4. 未來的挑戰與機遇

盡管面臨著封裝翹曲等挑戰,但PoP封裝技術的超薄化趨勢為行業帶來了更多的機遇。隨著技術的進步和材料的優化,翹曲控制將成為未來PoP封裝技術發展的一個重要方向。同時,隨著便攜式移動設備的需求不斷增加,PoP封裝技術在小型化和薄型化方面的優勢將得到更大的發揮。

總的來說,未來POP封裝的發展趨勢將是超薄化、技術創新和材料優化,但同時也需要面對封裝翹曲等挑戰。

五、c:

PoP堆疊芯片/Sip系統級封裝在mm級別間距進行焊接,助焊劑作用后留下的活性劑等吸濕性物質,較小的層間距如存有少量的吸濕性活性劑足以占據相對較大的芯片空間,影響芯片可靠性。要將有限的空間里將殘留物帶離清除,清洗劑需要具備較低的表面張力滲入層間芯片,達到將殘留帶離的目的。合明科技研發的清洗劑具有卓越的滲入能力,以確保芯片間殘留活性劑被徹底清除。

合明科技為您提供PoP堆疊芯片水基清洗全工藝解決方案。

針對先進封裝產品芯片焊后封裝前,基板載板焊盤、電子制程精密焊后清洗的不同要求,合明科技在水基清洗方面有比較豐富的經驗,對于有著低表面張力、低離子殘留、配合不同清洗工藝使用的情況,自主開發了較為完整的水基系列產品,精細化對應涵蓋從半導體封裝到PCBA組件終端,包括有水基清洗劑和半水基清洗劑,堿性水基清洗劑和中性水基清洗劑等。具體表現在,在同等的清洗力的情況下,合明科技的兼容性較佳,兼容的材料更為廣泛;在同等的兼容性下,合明科技的清洗劑清洗的錫膏種類更多(測試過的錫膏品種有ALPHA、SMIC、INDIUM、SUPER-FLEX、URA、TONGFANG、JISSYU、HANDA、OFT、WTO等品牌;測試過的焊料合金包括SAC305、SAC307、6337、925等不同成分),清洗速度更快,離子殘留低、干凈度更好。

想了解更多關于先進封裝產品芯片清洗的內容,請訪問我們的“先進封裝產品芯片清洗”產品與應用!

合明科技運用自身原創的產品技術,滿足芯片封裝工藝制程清洗的高難度技術要求,打破國外廠商在行業中的壟斷地位,為芯片封裝材料全面國產自主提供強有力的支持。

推薦使用合明科技水基清洗劑產品。

![[x]](/template/default/picture/closeimgfz1.svg)