合明科技分享:SOP封裝工藝,SOP封裝制程,SOP Process

SOP封裝工藝,SOP封裝制程,SOP Process

今天小編跟大家分享一篇關于SOP封裝工藝,SOP封裝制程,SOP Process的相關內容,希望能對大家有所幫助!

小外形封裝器件(Small Outine Package, SOP)屬于引腳從封裝體兩側子出呈翼狀的表面貼裝器件,其封裝結構分 為嵌人式和外露式兩種。SOP的標準引腳節距為 1.27mm,引腳數為 6-64。 SOP是市場上用量較大的封裝形式之一,SOP是在DIP基礎上發展而來的,衍生出的封裝形式有“丁”形引腳小外形封裝(SOJ)、薄小外形封裝(TSOP)、帶散熱片的小外形封裝 (HSOP)、裸露焊盤的小外形封裝(ESOP)、微小外形封裝(MSOP)、甚小外形封裝 (VSOP)、縮小型 SOP (SSOP)、薄的縮小型 SOP 封裝 (TSSOP)、裸露焊盤薄的微小外形封裝(EMSOP)、裸露焊盤薄的縮小型 SOP (ETSSOP)。這些封裝的引腳節距通常在0.40~1.27mm 的范圍內。

SOP較DIP、SiP 最明顯的區別在于,DIP 和 SiP 的引腳是直插式的,SOP的引腳是呈翼狀的表面貼裝式的。其主要優點如下:體積小,由于SOP與相同引腳數的DIP和SIP相比,厚度大大降低,引腳節距至少減少50%;與DIP和SIP相比,SOP衍生的封裝類別較多;SOP的芯片與引腳之間的連線短,寄生電容要比DIP的小;裸露焊盤封裝散熱效果更好。

下圖所示為 SOP、SSOP、ISSOP 產品圖

下圖所示為 ESOP、ETSSOP 產品圖

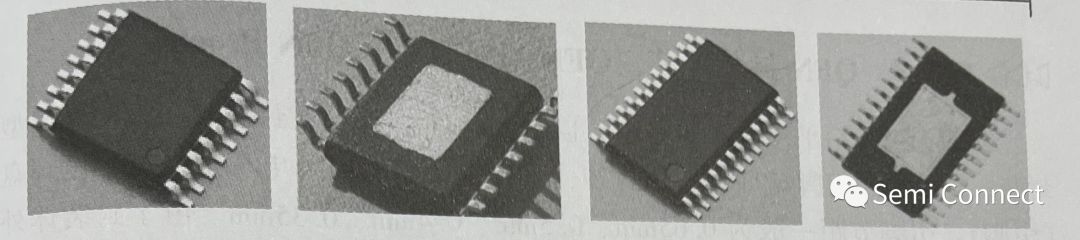

SOP封裝工藝是一種表面貼裝型(SMD)封裝制造工藝。SOP 封裝工藝流程為,首先減薄、劃片,然后將IC芯片粘貼在SOP引線框架的載體上,經過烘烤后,鍵合(打線)使芯片與芯片、芯片與內引腳相連接,再經過塑封將芯片鍵合絲、內引腳等包封,最后通過后固化、打標、電鎮、切筋成型、測試,完成整個SOP生產工藝過程。

SOP封裝工藝標準流程如下圖所示。

(1)減薄:己背金(背銀)的圓片不減薄。非背金(背銀)的圓片采用粗磨、精磨方法將原始圓片減薄。

(2)劃片:根據封裝需要,選擇普通藍膜、DAF (Die Attach Film)膜CDAF ( Conductive Die Attach Film)膜或 UV ( Ultra-violet Rays Fim)膜。目前劃片主要采用金鋼石刀片機械切割或激光切割工藝。

(3)裝片:采用黏片膠、膠膜片及 UV 膜上芯了種工藝。

(4)鍵合:即打線,焊線有金線、銅線、銀合金線和鋁線等材料,采用超聲波熱鍵合工藝。

(5)塑封:SOP 采用注射式成型工藝。

(6)后固化:使用烘箱對塑封后的產品進行高溫烘烤。

(7)打標:在產品正面使用激光打標機生成產品標志 (舊稱“打印”)。

(8) 電鍍:采用純錫電沉積工藝。錫化后,需要對產品進行烘烤。

(9)切筋成型:在切筋成型一體機上,先沖廢料、切去中筋,然后成型,自勁人管。

(10)測試:采用管裝或編帶一體化測試技術。

以上是關于SOP封裝工藝,SOP封裝制程,SOP Process的相關內容,希望能您你有所幫助!

想要了解關于POP堆疊芯片清洗的相關內容,請訪問我們的“POP堆疊芯片清洗”專題了解相關產品與應用 !

合明科技是一家電子水基清洗劑 環保清洗劑生產制造商,其產品覆蓋電子加工過程整個領域。歡迎使用合明科技水基清洗劑產品!

【閱讀提示】

以上為本公司一些經驗的累積,因工藝問題內容廣泛,沒有面面俱到,只對常見問題作分析,隨著電子產業的不斷更新換代,新的工藝問題也不斷出現,本公司自成立以來不斷的追求產品的創新,做到與時俱進,熟悉各種生產復雜工藝,能為各種客戶提供全方位的工藝、設備、材料的清洗解決方案支持。

【免責聲明】

1. 以上文章內容僅供讀者參閱,具體操作應咨詢技術工程師等;

2. 內容為作者個人觀點, 并不代表本網站贊同其觀點和對其真實性負責,本網站只提供參考并不構成投資及應用建議。本網站上部分文章為轉載,并不用于商業目的,如有涉及侵權等,請及時告知我們,我們會盡快處理;

3. 除了“轉載”之文章,本網站所刊原創內容之著作權屬于合明科技網站所有,未經本站之同意或授權,任何人不得以任何形式重制、轉載、散布、引用、變更、播送或出版該內容之全部或局部,亦不得有其他任何違反本站著作權之行為。“轉載”的文章若要轉載,請先取得原文出處和作者的同意授權;

4. 本網站擁有對此聲明的最終解釋權。