摩爾定律失效,Chiplet技術被“寄予厚望”

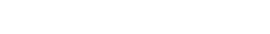

在探討Chiplet技術(小芯片)之前,摩爾定律是繞不開的話題。戈登·摩爾先生在1965 年提出了摩爾定律:每年單位面積內的晶體管數量會增加一倍,性能也會提升一倍。這意味著,在相同價格的基礎上,能獲得的晶體管數量翻倍。不過,摩爾先生在十年后的1975年,把定律的周期修正為24個月。至此,摩爾定律已經影響半導體行業有半個世紀。

圖片來源:芯耀輝

隨著集成電路技術的不斷演進,半導體行業發現摩爾定律在逐漸失效。上圖右上部分是英特爾x86 CPU 1970-2025年的演化歷史,可看出每顆芯片的晶體管數量持續增加(右上深藍色線條),但時鐘速度(右上天藍色線條)和熱設計功耗(右上灰色線條)自2005年之后就變化不大。于此同時,受先進工藝高成本支出的影響,晶體管成本降幅在2012年后趨緩,甚至越往后還有成本增加的趨勢。

從上圖右下的統計數據可看出,芯片制程在持續微縮和演進,晶體管數也在相應的增長。在2019年以前,單芯片晶體管數量和工藝幾何尺寸演進,一直與摩爾定律高度相關。因為單位面積內的晶體管數量,每一周期就會增加一倍,所以在理想情況下,Die的尺寸可保持不變。但是據右下綠色標識的區域顯示,可以看到單芯片Die尺寸在日趨增大,這也從另一個角度說明,單芯片晶體管數量的增加,也有Die增大的原因所致。由于Die尺寸的增長,受光罩尺寸、工藝良率等因素制約,這代表通過加大Die Size來提升單芯片算力已經越來越困難。

總而言之,隨著集成電路技術的發展和演進,每24個月已經很難讓單位面積內的晶體管數量翻倍。這意味著,現在芯片性能的提升遭遇了瓶頸,性能無法單純由工藝技術驅動,也需要由架構創新來驅動。因此,業界必須找到新的解決方案。

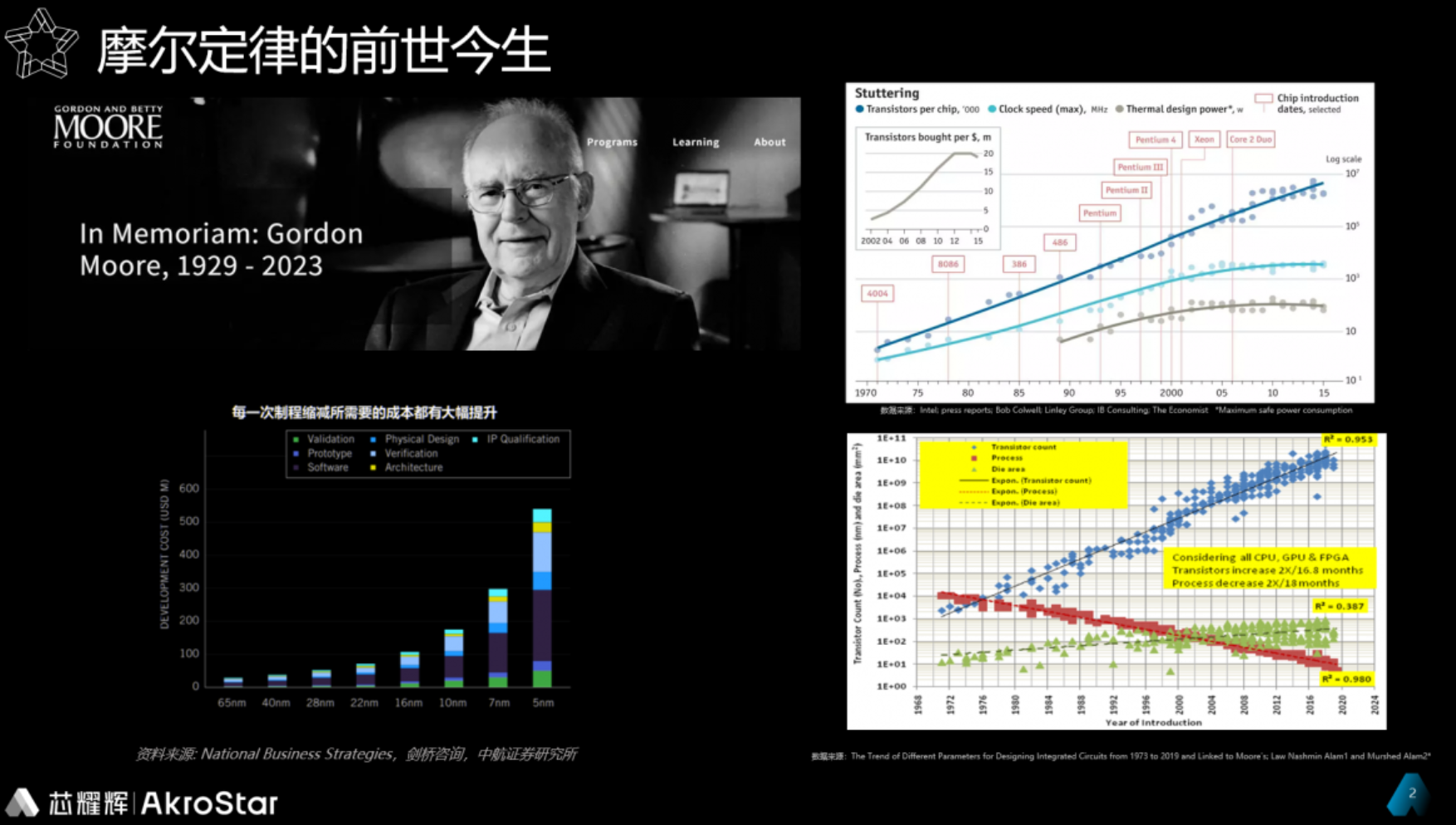

基于Chiplet技術的芯片結構示意 圖源:英特爾

在摩爾定律逐漸失效的情況下,Chiplet技術在半導體行業應運而生。整體來看,Chiplet具備高集成度、高良率、低成本三大特點,它被視為延續摩爾定律的關鍵技術。

Chiplet技術并不是創新概念,它很早就被提出來了,只是市場應用需求沒有發展到這一步,因此長期處于“隱身”狀態。Chiplet通常被翻譯為“芯粒”或“小芯片”。單從字面意義上可以理解為更為“粒度更小的芯片”。通過半導體制造將若干“芯粒”集成,而非純粹封裝集成,以此形成復雜功能芯片,可以突破單芯片光刻面積的瓶頸,突破設計周期制約等。

舉例來說,在一顆7nm制程芯片中,一些次要的模塊可以用如22nm的制程做成Chiplet,再“拼裝”至7nm芯片上,原理如同搭積木一樣,這樣可以減少對7nm工藝制程的依賴。

Chiplet技術相關的半導體國內企業包括大港股份、芯原股份、中京電子、同興達、蘇州固锝、中富電路、朗迪集團、晶方科技、長電科技、通富微電、華天科技、華峰測控等。

Chiplet技術優勢

Chiplet可以把傳統的單芯片設計方案改成多芯片(Die)進行設計,并利用先進封裝工藝進行集成。它的優勢主要有以下幾點:

1、提升芯片制造良率,由于良率和芯片的面積有關,面積越大,良率大概率會越低,因此,把一個大芯片分拆成多個小芯片(Die)設計并分別投片,就可以提高良率,良率提升,還可以降低制造成本。

2、以不同的工藝實現一顆芯片,用先進制程制造CPU等計算核心,用相對成熟的制程制造I/O之類的功能塊,可以很好地控制整體成本。

3、設計更加靈活,設計出的Die,通過不同的組合方式,可設計出不同功能的芯片。

Chiplet技術經過發展,國際上出現了一些Chiplet標準,主流標準包括XSR、BOW、OpenHBI、UCIe。雖然有這么多好處,但Chiplet技術并不成熟,各種Die、接口I/O、總線等,與常規的SoC有很大區別,需要制定統一的標準,從而使產業鏈上的設計、制造、封裝等廠商能按照標準操作,才能實現高效、規模化生產。因此,UCIe和ACC 1.0等行業規范相繼推出。

Chiplet面臨的挑戰

雖然Chiplet優點很多,同時也面臨著很多問題,會阻礙其發展,例如:

一,應用場景,并不是所有應用類型的芯片都適合做Chiplet,目前來看,CPU、GPU等處理器最適合做Chiplet,而且是在高性能應用領域,像智能手機等消費類電子設備用的芯片,很少需要采用Chiplet設計;

二,成本,只有傳統SoC成本達到一定量級,改用Chiplet設計才劃算;

三、良率問題;

四、測試問題。

近期,中國成立了自己的Chiplet(小芯片,或芯粒)聯盟,由多家芯片設計,IP,以及封裝、測試和組裝服務公司組成,同時推出了相應的互連接口標準ACC 1.0。

在美國打壓,中國尋求半導體產業鏈關鍵環節自主可控的當下,這一聯盟的成立,頗有與由AMD、Arm、英特爾、臺積電和ASE(日月光)主導的UCIe聯盟分庭抗禮的意味。

從技術層面來看,Chiplet的價值和發展前景已經在全球半導體界達成普遍共識。總體而言,Chiplet有很好的應用和發展前景,但它不是中國半導體業沖刺國際先進水平的靈丹妙藥。要想提升全行業競爭力,還是要有決心和毅力,秉持十年磨一劍的精神,全方位發展本土半導體材料、設備、IP、設計和制造水平。

【閱讀提示】

以上為本公司一些經驗的累積,因工藝問題內容廣泛,沒有面面俱到,只對常見問題作分析,隨著電子產業的不斷更新換代,新的工藝問題也不斷出現,本公司自成立以來不斷的追求產品的創新,做到與時俱進,熟悉各種生產復雜工藝,能為各種客戶提供全方位的工藝、設備、材料的清洗解決方案支持。

【免責聲明】

1. 以上文章內容僅供讀者參閱,具體操作應咨詢技術工程師等;

2. 內容為作者個人觀點, 并不代表本網站贊同其觀點和對其真實性負責,本網站只提供參考并不構成投資及應用建議。本網站上部分文章為轉載,并不用于商業目的,如有涉及侵權等,請及時告知我們,我們會盡快處理;

3. 除了“轉載”之文章,本網站所刊原創內容之著作權屬于合明科技網站所有,未經本站之同意或授權,任何人不得以任何形式重制、轉載、散布、引用、變更、播送或出版該內容之全部或局部,亦不得有其他任何違反本站著作權之行為。“轉載”的文章若要轉載,請先取得原文出處和作者的同意授權;

4. 本網站擁有對此聲明的最終解釋權。